Cpld

CPLD, czyli Complex Programmable Logic Device, to zaawansowany typ programowalnych układów logicznych, które łączą w sobie elastyczność programowania z dużą gęstością logiczną i stosunkowo prostą architekturą. Dziś wyjaśnię Ci, czym dokładnie jest CPLD, jak działa i gdzie znajduje zastosowanie w nowoczesnej elektronice cyfrowej. Po drodze poruszymy także tematy pokrewne, które pomogą Ci lepiej zrozumieć, jak CPLD wpisuje się w świat układów programowalnych, takich jak FPGA i PROM.

Podstawowa budowa i działanie CPLD

CPLD składa się z kilku bloków logicznych zwanych macierzami logicznymi (logic arrays), które można zaprogramować do realizacji określonych funkcji cyfrowych. W przeciwieństwie do FPGA, które mają strukturę matrycową o bardzo dużej liczbie elementów, CPLD charakteryzują się bardziej modularną budową oraz mniejszą ilością komórek logicznych, ale z silniejszymi blokami funkcjonalnymi.

Wewnątrz CPLD znajdują się:

- Programowalne bramki logiczne (AND, OR, NOT)

- Macierze połączeń umożliwiające konfigurowanie ścieżek sygnałowych

- Rejestry i przerzutniki do realizacji funkcji pamięciowych i synchronizacji

- Wejścia/wyjścia programowalne (I/O), które można dostosować do różnych standardów logicznych

Dzięki tej budowie CPLD pozwalają na zaprojektowanie i implementację złożonych funkcji cyfrowych, jak dekodery, multipleksery, kontrolery czy układy sterujące, bez potrzeby stosowania wielu oddzielnych układów.

Programowanie i konfiguracja

Programowanie CPLD odbywa się najczęściej za pomocą języków opisu sprzętu takich jak VHDL czy Verilog. Dzięki temu projektant może opisać w kodzie sprzętowym wymagane funkcje logiczne, które zostaną później przetłumaczone na konfigurację układu. To daje ogromną swobodę i skraca czas projektowania w porównaniu do tradycyjnych metod opartych na układach dyskretnych lub niestandardowych ASIC.

Konfiguracja CPLD jest trwała, co oznacza, że raz zaprogramowany układ zachowuje swoją funkcję nawet po odłączeniu zasilania. W przeciwieństwie do niektórych FPGA, które wymagają ładowania konfiguracji przy każdym uruchomieniu, CPLD oferują stabilność i niezawodność, co jest cenne w zastosowaniach przemysłowych.

Zastosowania CPLD

CPLD są szeroko stosowane w miejscach, gdzie potrzebna jest umiarkowana złożoność układu cyfrowego, ale z szybkim czasem reakcji i niezawodnością. Typowe przykłady zastosowań to:

- Implementacja układów sterujących i synchronizujących

- Mostki logiczne i interfejsy między różnymi standardami komunikacyjnymi

- Proste kontrolery i układy zabezpieczające

- Układy zastępujące tradycyjne bramki i multipleksery, zmniejszające liczbę elementów na płytce

- Szybkie prototypowanie i testowanie rozwiązań sprzętowych

Ze względu na stabilność konfiguracji, CPLD często znajdziemy w systemach przemysłowych, motoryzacyjnych, a także w elektronice konsumenckiej, gdzie niezawodność jest kluczowa.

CPLD a FPGA – różnice i uzupełnienia

Choć CPLD i FPGA to oba typy programowalnych układów logicznych, różnią się architekturą, skalą oraz zastosowaniem. CPLD oferują mniejszą gęstość logiczną i prostszą architekturę, co przekłada się na szybszy czas reakcji i niższe zużycie energii. FPGA z kolei mają większą elastyczność i możliwości, szczególnie przy bardzo złożonych układach, które wymagają dużej liczby logiki programowalnej i bloków DSP.

Jeśli pamiętasz z wczorajszego materiału o PROM i PAL, CPLD można uznać za ich bardziej zaawansowaną i złożoną ewolucję. Warto też zauważyć, że wiele nowoczesnych projektów używa obu tych układów równocześnie, wykorzystując CPLD do funkcji kontrolnych i FPGA do obliczeń sygnałowych.

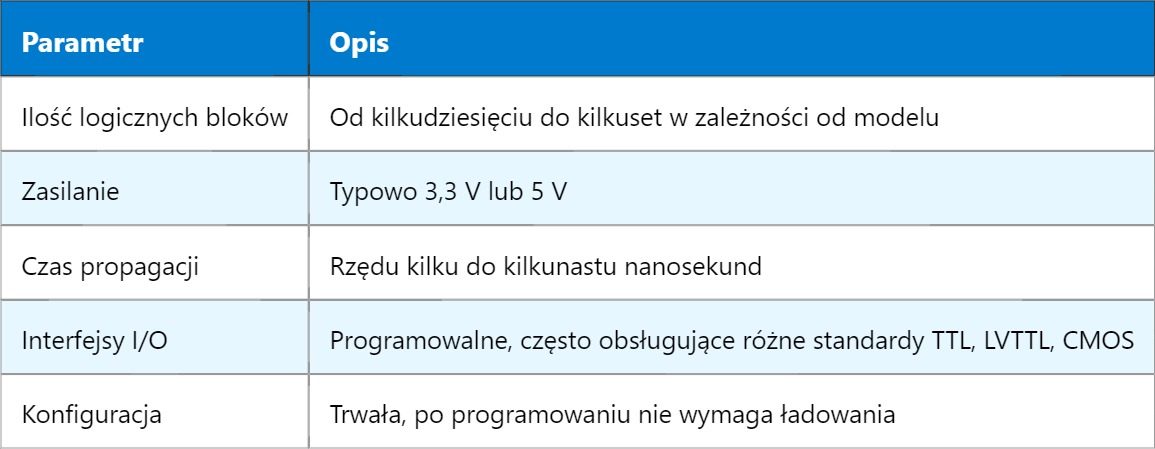

Parametry techniczne CPLD

Projektowanie i narzędzia wspomagające

Projektowanie CPLD wymaga użycia dedykowanych narzędzi programistycznych, które pozwalają na opisanie układu, symulację i programowanie. Firmy takie jak Xilinx, Intel (wcześniej Altera) czy Lattice oferują środowiska do projektowania, które integrują edytory kodu VHDL/Verilog, symulatory oraz programatory sprzętowe.

W trakcie projektowania ważne jest również testowanie funkcjonalne i timingowe, aby upewnić się, że sygnały logiczne działają zgodnie z oczekiwaniami w docelowej aplikacji. Często używa się symulacji oraz analizatorów logicznych do debugowania sprzętu.

Jeśli porównasz ten temat z FPGA, które omawialiśmy ostatnio, zauważysz, że CPLD to świetne rozwiązanie dla mniej skomplikowanych układów, gdzie liczy się szybkość reakcji i prostota. Jutro możemy przyjrzeć się bliżej temu, jak FPGA i CPLD uzupełniają się w projektach embedded, zwłaszcza w kontekście systemów czasu rzeczywistego.